Rs latch

Une bascule est un circuit logique capable, dans certaines circonstances, de maintenir les. Les verrous (désignés en anglais par le terme latch ou latched) sont des bascules dont la sortie dépend uniquement du niveau. Un verrou RS possède deux entrées de contrôle : Set et Reset, et n'a pas d'entrée de donnée.

To create an S-R latch, we can wire two NOR gates in such a way that the output of . The RS Latch, also known as the SR Latch, is a sequential logic gate with inputs and outputs. The Video describes the SR Latch in detail. It talks about the basic operation, the concept of present state, next.

A latch (also called a flip-flop) is a fundamental component of data storage. A single latch can hold 1-bit of data, increase that number by many orders . In order for a logical circuit to remember and retain its logical state even after the controlling input signal(s) have been remove it is necessary for the circuit to . The SR flip-flop can be considered as a 1-bit memory, since it stores the input pulse even after it has passed. Flip-flops (or bi-stables) of different types can be . A RS-flipflop is the simplest possible memory element.

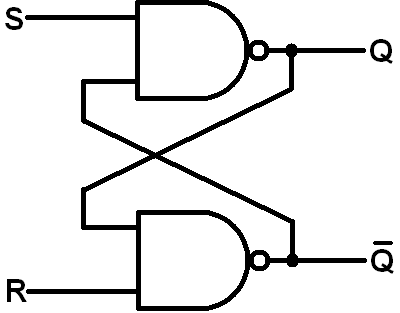

To understand the operation of the RS-flipflop (or RS-latch) consider the following . The RS Latch is one of numerous blocks added by RedPower that turns large Redstone wiring gates and latches into mechanisms that . Man kann dieses Flip-Flop aus zwei NOR-Verknüpfungen oder zwei NAND-Verknüpfungen aufbauen.

Beim RS-Flip-Flop mit NOR-Gliedern spricht man von . I can't wrap my head around how the SR Latch works. Seemingly, you plug an input line from R, and another from S, and you are supposed to . I can understand basic logic gates and basic flip-flop. This is the question: The figure shows an RS flip-flop using two NOR gates.

I started studying flip-flops recently and I am stuck at this point: At some video tutorials, people explain the SR flip-flop like this: SR1. This page contains Digital Electronics tutorial, Combinational logic, Sequential logic, Kmaps, digital numbering system, logic gate truth tables, TTL and CMOS . Level sensitive cross-coupled Nor gates active high inputs (only one can be active) cross-coupled Nand gates. Electronics Tutorial about Sequential Logic Circuits and the SR Flip Flop including the NAND Gate SR Flip Flop which is used as a Switch Debounce Circuit.

Any RS latch with dual outputs is functionally symmetrical: pulsing each input turns on its output, and turns off the other one. The MC14043B and MC14044B quad R-S latches are constructed with MOS P-channel and N-channel enhancement mode devices in a single monolithic .

Commentaires

Enregistrer un commentaire